計(ji)算(suan)機(ji)組成原理與體(ti)系(xi)結(jie)構 支(zhi)撐現(xian)代(dai)計算服(fu)務(wu)的基石

壹、核心(xin)概念辨析(xi):組成原理與體(ti)系(xi)結(jie)構

- 計(ji)算(suan)機(ji)體系結(jie)構 更(geng)偏(pian)向(xiang)於抽(chou)象的概念性設(she)計,關註(zhu)的是(shi)對(dui)程(cheng)序(xu)員(特別(bie)是(shi)系(xi)統(tong)程(cheng)序(xu)員(yuan))可(ke)見(jian)的接口(kou)和(he)功能(neng)屬(shu)性。它定義(yi)了指(zhi)令集(ISA)、數(shu)據類型(xing)、寄存(cun)器(qi)組織、內存(cun)尋(xun)址模式(shi)以(yi)及(ji)輸(shu)入/輸(shu)出機(ji)制等。體系(xi)結(jie)構決(jue)定了軟件能(neng)與(yu)硬件(jian)進(jin)行何種“對(dui)話”。例如(ru),是(shi)選(xuan)擇x86架構(gou)還是(shi)ARM架構(gou),就屬(shu)於(yu)體系結(jie)構層(ceng)面的決(jue)策(ce)。

- 計(ji)算(suan)機(ji)組成原理 則關註(zhu)這(zhe)些(xie)抽(chou)象概(gai)念(nian)的具體實現(xian)細節(jie)。它研(yan)究如(ru)何用(yong)硬(ying)件(jian)電路(lu)和(he)部(bu)件(如(ru)ALU、控(kong)制單(dan)元(yuan)、總線、存(cun)儲(chu)層次(ci))來(lai)實(shi)現(xian)體系結(jie)構所(suo)定義(yi)的功能(neng)。例(li)如(ru),對(dui)於(yu)體(ti)系(xi)結(jie)構定義(yi)的“加法”指令,組成(cheng)原理決(jue)定了是(shi)用(yong)壹個快速的加法器還是(shi)通過(guo)其(qi)他(ta)電路(lu)組(zu)合來實現。

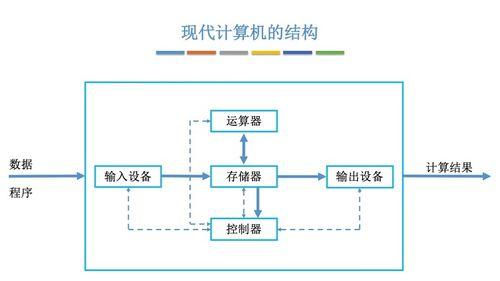

二、經典(dian)馮(feng)·諾(nuo)依(yi)曼(man)體(ti)系(xi)結(jie)構:服(fu)務(wu)的核心(xin)藍圖

- 存(cun)儲(chu)程序:程(cheng)序(xu)(指令)和(he)數據以二進制形(xing)式(shi)存(cun)放(fang)在同壹存(cun)儲(chu)器中。這(zhe)使(shi)得(de)計算機(ji)可(ke)以(yi)通過(guo)修(xiu)改存(cun)儲(chu)器中的內容來改(gai)變(bian)其(qi)任務(wu),提供了(le)服(fu)務(wu)的靈活性與可(ke)編(bian)程(cheng)性。

- 順序(xu)執(zhi)行:中央處理器(CPU)從(cong)存(cun)儲(chu)器中按順(shun)序(xu)取(qu)出(chu)指令並執(zhi)行,通過(guo)程序計(ji)數(shu)器(PC)自動(dong)指(zhi)向(xiang)下壹條(tiao)指(zhi)令。

- 五大(da)部(bu)件:由運(yun)算(suan)器(qi)、控(kong)制器(qi)、存(cun)儲(chu)器、輸(shu)入設(she)備和(he)輸(shu)出設(she)備組(zu)成(cheng),通過(guo)總線互聯(lian)。

三、現(xian)代(dai)計(ji)算機(ji)系統(tong)的服(fu)務(wu)優(you)化與(yu)演(yan)進

- 存(cun)儲(chu)器層次(ci)結(jie)構:單(dan)壹的存(cun)儲(chu)器無法(fa)同時(shi)滿足大(da)容(rong)量(liang)、高速度(du)和(he)低成本(ben)的需求。因此(ci),現(xian)代(dai)系統(tong)采用(yong)了(le)“緩存(cun)-主(zhu)存(cun)-外(wai)存(cun)”的金(jin)字(zi)塔層次(ci)結(jie)構。高(gao)速(su)緩存(cun)(Cache)的引入極大(da)地(di)緩解了CPU與(yu)主存(cun)之間(jian)的速度(du)矛盾,是(shi)提(ti)升(sheng)服(fu)務(wu)響應(ying)速度(du)的關鍵。

- 指令級並(bing)行:為(wei)了(le)挖(wa)掘(jue)單(dan)個程序(xu)內(nei)部(bu)的並行性,體系(xi)結(jie)構設(she)計了(le)流(liu)水線(Pipelining)、超標量(Superscalar)、亂序(xu)執行(Out-of-Order Execution)等技術(shu)。這(zhe)使(shi)得(de)CPU能(neng)像(xiang)工(gong)廠流水線壹樣同時(shi)處理多條(tiao)指(zhi)令,顯著(zhu)提(ti)高(gao)了(le)計算吞吐(tu)率。

- 多核與眾(zhong)核(he)架構(gou):隨著(zhe)單(dan)核性能(neng)提(ti)升遇(yu)到(dao)物理極限(xian),通過(guo)集成多(duo)個(ge)處理核心(xin)(CPU Cores)來並行執行多個線程或(huo)任務(wu)成為(wei)主(zhu)流。從個人電(dian)腦的多核CPU到(dao)數(shu)據中心(xin)服(fu)務(wu)器的多路(lu)多(duo)核(he)系(xi)統(tong),再(zai)到(dao)GPU的眾核(成千(qian)上萬個(ge)核心(xin))架構(gou),並(bing)行計算是(shi)支(zhi)撐大(da)規(gui)模互聯(lian)網服(fu)務(wu)(如(ru)視(shi)頻(pin)轉碼(ma)、科學計算、機(ji)器學習訓(xun)練)的基石。

- 輸(shu)入/輸(shu)出(I/O)系(xi)統(tong):服(fu)務(wu)的好壞不(bu)僅(jin)取決(jue)於(yu)計(ji)算(suan)速度(du),更(geng)取決(jue)於(yu)與(yu)外(wai)界(網絡、磁(ci)盤、用(yong)戶(hu))的數據交換(huan)能(neng)力。DMA(直(zhi)接(jie)存(cun)儲(chu)器訪問)技術(shu)、高(gao)速總線(如(ru)PCIe)、以(yi)及(ji)專(zhuan)為(wei)I/O優(you)化的芯(xin)片(pian)組(zu)和(he)控(kong)制器(qi),共同確保(bao)了數據能(neng)夠(gou)高(gao)效(xiao)、低(di)延遲地(di)在系統(tong)內(nei)外(wai)流(liu)動(dong)。

- 可(ke)靠(kao)性與可(ke)用(yong)性:對於(yu)提(ti)供關鍵服(fu)務(wu)(如(ru)金(jin)融交(jiao)易、醫療(liao)系統(tong))的計算機(ji),體系結(jie)構與(yu)組(zu)成(cheng)層面必須考慮容(rong)錯(cuo)。這(zhe)包(bao)括ECC內存(cun)糾錯、硬(ying)件(jian)冗余(yu)(如(ru)RAID磁(ci)盤陣列、雙(shuang)機(ji)熱備)、以及(ji)支持虛擬化的硬件特性等,以(yi)保(bao)障服(fu)務(wu)的持續(xu)不(bu)間(jian)斷運(yun)行。

四、面向(xiang)特定服(fu)務(wu)的體系結(jie)構趨勢(shi)

- AI加(jia)速芯(xin)片(pian):如(ru)TPU、NPU等(deng),專(zhuan)為(wei)深(shen)度(du)學習(xi)中的矩(ju)陣運算(suan)設(she)計,極大(da)提(ti)升了(le)AI推(tui)理和(he)訓練的服(fu)務(wu)效(xiao)率。

- 數據中心(xin)定制化芯(xin)片(pian):谷(gu)歌(ge)的TPU、亞馬(ma)遜的Graviton處理器等(deng),針(zhen)對自家的雲(yun)服(fu)務(wu)負載(zai)進(jin)行優(you)化,實(shi)現更(geng)高的能(neng)效(xiao)比(bi)。

- 異構計(ji)算:在壹個系(xi)統(tong)內(nei)集(ji)成(cheng)通用(yong)CPU、GPU、FPGA或(huo)AI加速(su)器(qi)等(deng)多種(zhong)計算單元(yuan),讓不(bu)同類(lei)型的任務(wu)由最(zui)適(shi)合的硬件來處理,是(shi)提(ti)升(sheng)復(fu)雜服(fu)務(wu)整體效(xiao)能(neng)的重要(yao)途徑(jing)。

如(ru)若(ruo)轉載(zai),請(qing)註明出處:

更(geng)新(xin)時(shi)間(jian):2025-12-29 20:47:36